The DS1100L is a 3.3V version of the DS1100. It features operation in the 3.0V to 3.6V range. The DS1100L series delay line has five equally spaced taps, providing delays from 4ns to 500ns. These devices are packaged with surface mount to save PCB area.

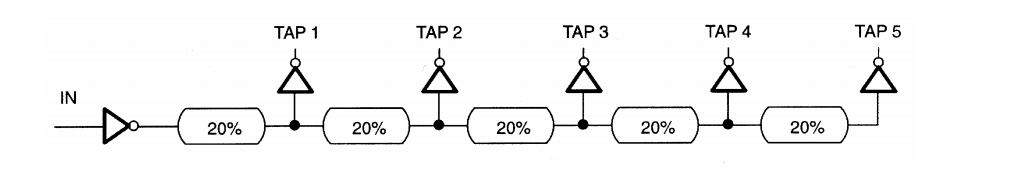

Logic diagram

The combination of 100% silicon delay lines and industry-standard µMAX and SO packages achieves low cost and superior reliability compared to hybrid technologies. The DS1100L 5-tap silicon delay line reproduces the input logic state of the output after a fixed delay specified by the part number extension behind the dotted line.

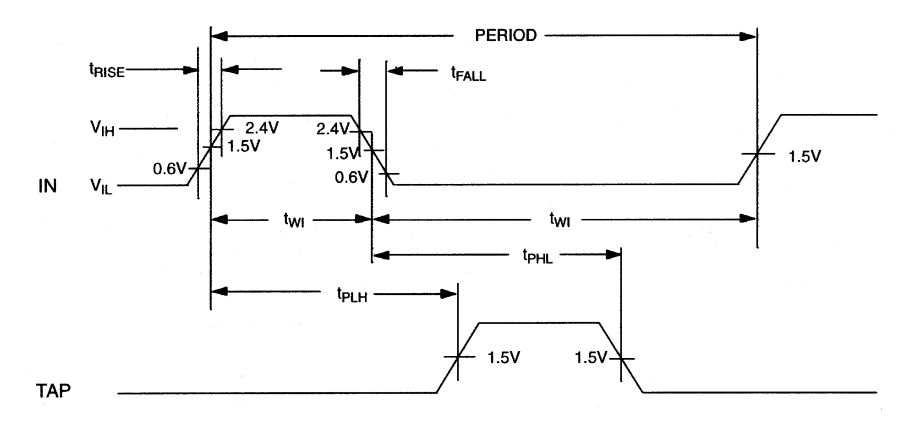

Sequence diagram

The DS1100L is designed to reproduce the leading and trailing edges with the same accuracy. Each tap is capable of driving up to 10 74LS loads. Standard products can be customized according to the special needs of customers.

Test circuit diagram

Product characteristics:

○All-silicon timing circuit

○Five times in equal distance

○The delay is stable and precise

○Front and back edge accuracy

○3.3V version of the DS1100

○Low power CMOS

○TTL / CMOS-Compatible

○Gas phase and IR weldable

○Custom delays are available

○Short prototype

○Commercial and industrial temperature ranges